Lec 13. Pipeline MIPS_2 (The Processor)

* datapaths / controllers

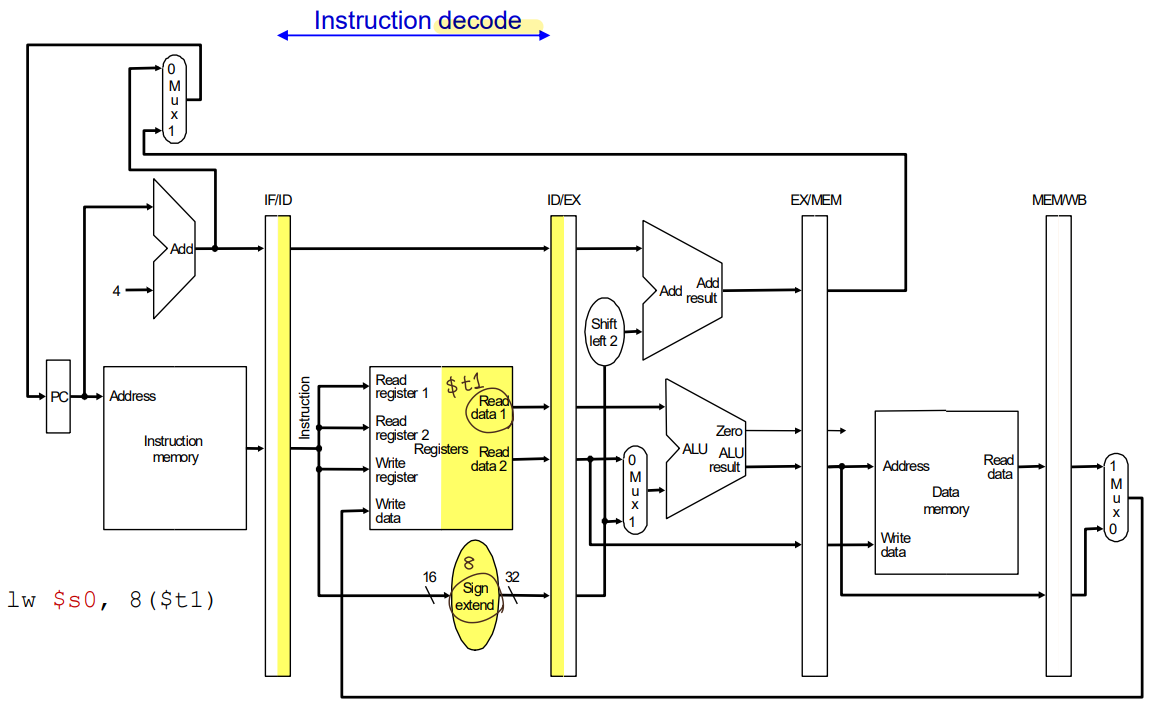

- Pipelined Datapath

flip-flop (datapath)

= pipeline register

: stage 구분용. 이전 stage의 값을 기억했다가 새로운 클럭(rising edge)일 때마다 다음 stage에 넘겨줌.

- lw

* WB 단계에서 주의할 점) Write register를 저장해두었다가 사용해야함!

: WB 단계에서 lw $s0, 8($t1) 명령어를 처리중인데, 그 시점에 Write register 에 접근하면

lw 명령어 이후에 fetch한 다른 명령어로 부터 나온 타겟($s0 이 아닌 것)을 가리킬 수 도 있음.

따라서 lw에서의 타겟을 알맞게 지칭하려면 예전에 Fetch/Decode 했던 내용을 기억해뒀다가 사용해야함.

- sw

* Control Unit

- Pipeline Control

What needs to be controlled in each stage?

-> IF : Instruction fetch, PC increment

-> ID : Instruction decode and operand fetch from register file and/or immediate

-> EX : RegDst, ALUop[1:0], ALUSrc

-> MA : Branch, MemRead, MenWrite

-> WB : MentoReg, RegWrite(WB시점에 사용, ID단계에 표기)

ID 시점에 Control Signal들이 생성되고, 필요할 때까지 pipeline register에 보관되다가

사용 후 (필요없어지면) 버려짐.

- Datapath with Control

- example

'CS > 3-1 컴구' 카테고리의 다른 글

| [컴퓨터구조] #15. Cache(1) (0) | 2022.05.29 |

|---|---|

| [컴퓨터구조] #14. Pipeline MIPS(3) (0) | 2022.05.20 |

| [컴퓨터구조] #12. Pipeline MIPS(1) (2) | 2022.05.11 |

| [컴퓨터구조] #11. Single-Cycle MIPS(2) (3) | 2022.04.23 |

| [컴퓨터구조] #10. Single-Cycle MIPS(1) (2) | 2022.04.13 |

댓글