Lec 3. MIPS Instructions_3 (Language of the Computer)

- Data Transfer Instructions

: CPU는 제한된 수의 레지스터를 가지고 있음. (MIPS는 일반 레지스터 32개)

그래서 CPU는 레지스터에 적은 양의 데이터만 보관 가능.

-> 데이터를 메모리에 담아두자! -> transfer data between memory and registers 하는 명령어 필요함!!

=> 그러한 명령어를 data transfer instructions 라고 부름.

레지스터는 32개밖에 없기때문에 각 레지스터마다 register name이 있어서 구분 가능,

메모리는 훨씬 크기때문에 각각의 name은 없고 memory address로 접근해야함.

- Memory Operands

Load (읽기) : memory -> register

Store (쓰기) : register -> memory

메모리는 byte-addressed. (한 칸이 1byte = 8bit)

word (4byte) 크기의 데이터를 읽고(lw) 쓸때(sw)는 메모리 시작주소가 4의 배수여야 함.

MIPS 는 Big Endian 임. (MSB가 least address에 위치)

- Endianness

Big Endian : most significant byte를 제일 작은 주소에 배치 ex) MIPS, SPARC

Little Endian : most significant byte를 제일 큰 주소에 배치 ex) x86, RISC-V

*most significant byte : 최상위 bit 8개

항상 4byte 읽기/쓰기만 한다면 endianness는 doesn't matter.

smaller size로 읽으면 it matters.

- Memory Operand Example

ex1) g = h + A[8]; //이때 A[8]을 레지스터에 전부 넣을 수 없다고 가정해보자.

g in $s1, h in $s2, base address(배열 시작 주소) of A in $s3

lw $to, 32($s3) # $s3에 담긴 주소로부터 32만큼 떨어진 곳에서 값을 읽어와서 $t0에 저장.

# 32인 이유? : A[0], A[1], ... A[8]의 주소가 word(4byte)단위로 증가하고 현재 A[8]을 보고있으므로

4 (element size) * 8 (index value) = 32 임.

add $s1, $s2, $t0

ex2) A[12] = h + A[8];

lw $t0, 32($s3)

add $t0, $s2, $t0

sw $t0, 48($s3) #48인 이유? : 4 (element size) * 12 (index value) = 48

- Immediate Operands

상수 덧셈 : 메인 메모리의 특정 주소들에 상수를 다 넣어두고 필요시 레지스터에 load해서 사용 -> 비효율적

lw $t0, AddrConstant4($s1) # $t0 = canstant 4

add $s3, $s3, $t0 # $s3 = $s3 + $t0

-> 해결책 _ 레지스터와 상수의 덧셈을 가능하게 했음!

addi $s3, $s3, 4

* subi 는 없음. addi $s2, $s1, -1 처럼 음수를 사용하면 됨! (instruction set 간소화)

- R-format

: 명령어의 3개 피연산자 모두 레지스터에 들어있음,

opcode와 funct로 명령어 구분

- I-format

: 명령어의 1개 피연산자는 명령어 자체에 들어있음. 그것을 immediates 라고 부름.

(레지스터나 메모리에 접근할 필요X),

opcode로 명령어 구분.

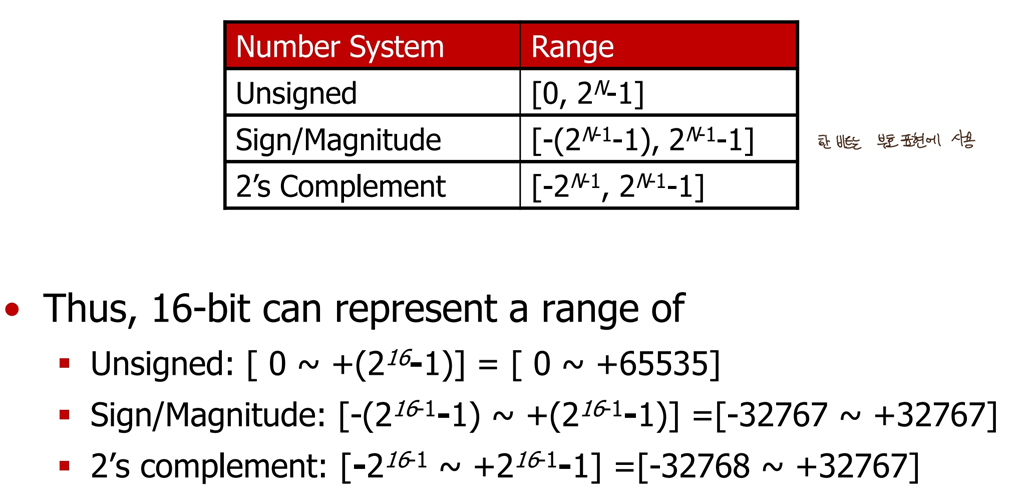

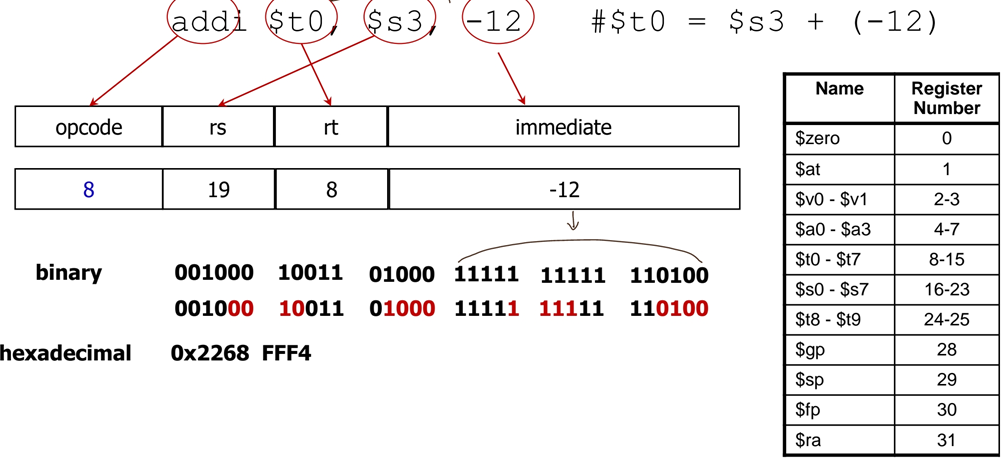

immediates는 16bit이고 2의 보수 체계로 작성된 수임.(-2^15 ~ +2^15-1)

*2의 보수 : flip all the bits and add 1

- Number System Comparison with N-bit

- addi

: I-format instruction

addi rt, rs, imm

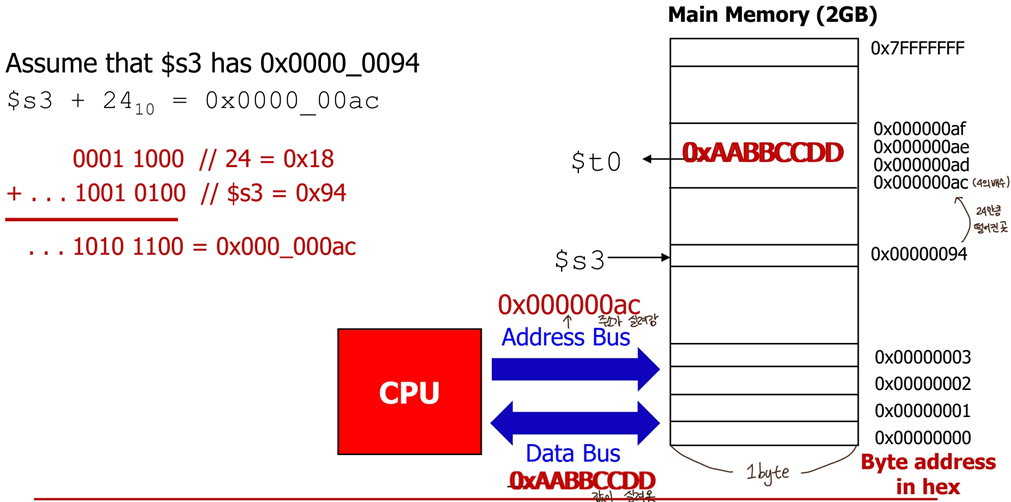

- lw

: I-format instruction, read a word (32bit) from memory and loads into a register

lw rt, address

the base is $s3 and the offset is 24.

immediate에는 offset이 담기며 그 수는 16bit 2's complement [-32768, 32767]

ex) lw $t0, 24($s3) # $t0 <= [$s3 + 24]

Address Bus를 통해 CPU에서 Main Memory로 $s3+24 이 전달됨

-> 전달받은 주소($s3에 담겨있는 주소로부터 24만큼 떨어진곳)에 있는 값이

Data Bus를 통해 Main Memory에서 CPU로 실려옴 -> 그 값이 $t0에 저장됨.

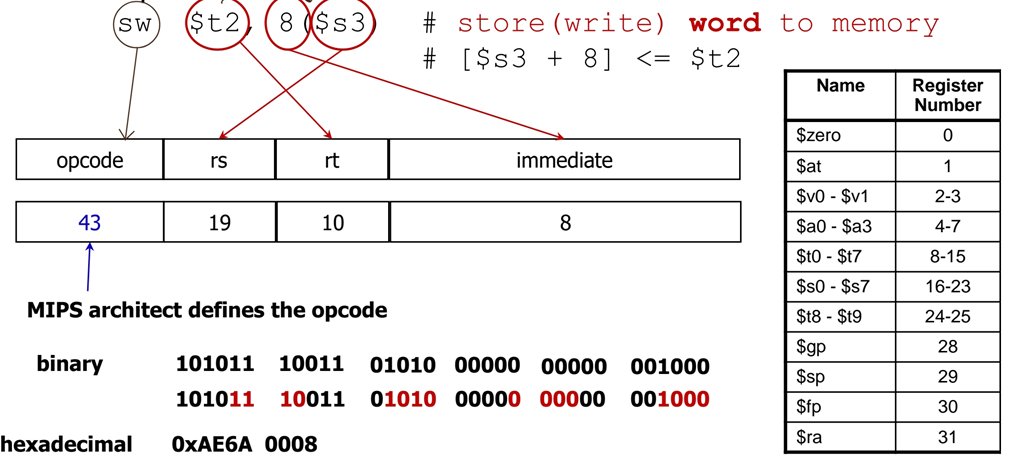

- sw

: I-format instruction, stores (writes) a word (32bit) from a register to main memory

sw rt, address

'CS > 3-1 컴구' 카테고리의 다른 글

| [컴퓨터구조] #6. MIPS 명령어(6) (10) | 2022.03.26 |

|---|---|

| [컴퓨터구조] #5. MIPS 명령어(5) (2) | 2022.03.23 |

| [컴퓨터구조] #4. MIPS 명령어(4) (0) | 2022.03.19 |

| [컴퓨터구조] #2. MIPS 명령어(2) (0) | 2022.03.11 |

| [컴퓨터구조] #0~1. 소개, MIPS 명령어(1) (2) | 2022.03.05 |

댓글